At the International Supercomputing Conference 2021, Intel has revealed new information about the 4th generation Xeon Scalable server processors, also known as Sapphire Rapids. One of the key features of the family will be a high-performance HBM (High Bandwidth Memory) cache buffer for some models.

Resource Inpact-Hardware, referring to its informants, reports that AMD can provide a symmetric answer. These are EPYC server processors, codenamed Genoa, based on the Zen 4 microarchitecture. Like the competitor’s solutions, some of the high-end EPYC processors will be equipped with HBM chips.

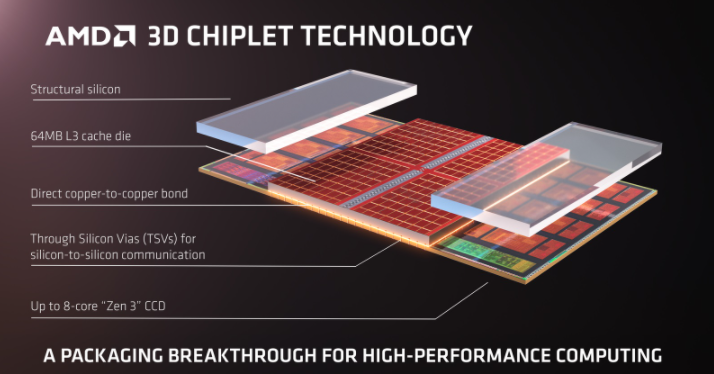

Apparently, the final decision at AMD regarding HBM has not yet been made and is in the process of discussion. Moreover, in the arsenal of the “reds” there is the 3D V-Cache technology, which allows to increase the amount of the L3 cache memory. In the case of server options, most likely, the bill will go to hundreds of megabytes, since for ordinary Ryzen 5000 3D V-Cache technology is able to add 64 MB or 128 MB of cache